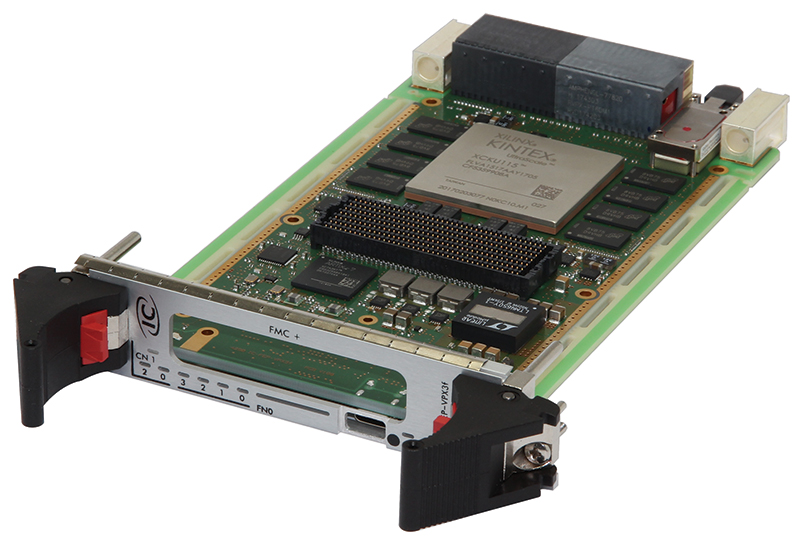

The First VITA 66.5 compliant 3U VPX Xilinx Kintex® UltraScale™ FPGA board, available on the market

Interface Concept, a leader in Commercial-Off-The-Shelf (COTS) solutions is announcing the IC-FEP-VPX3f board, a new high-speed 3U VPX FPGA board based on the Xilinx Kintex® UltraScale™ technology and designed for the signal-processing-intensive applications of high-performance embedded computing (HPEC) systems.

The IC-FEP-VPX3f board is the first VITA 66.5 compliant 3U VPX Xilinx Kintex® UltraScale™ FPGA board available today on the market. The VITA 66.5 standard enhances VPX capabilities by offering fiber optic interfaces on the board’s backplane connectors: the IC-FEP-VPX3f comes with 12 such full-duplex optical lanes.

Interface Concept has selected the LightCONEX™ LC 150G optical interconnect from Reflex Photonics to equip its IC-FEP-VPX3f, as it is the only full-duplex optical interconnect with 24-lane transceivers on the market. It provides bandwidth in excess of 150 Gbps, and delivers unprecedented performance to our FPGA VPX board.

The IC-FEP-VPX3f board integrates the following key devices: a user-programmable Xilinx Kintex® UltraScale™ FPGA (KU060, KU85 or KU115) based on the cutting-edge 20 nm technology and which provides higher performance than its predecessors while maintaining low power consumption; 8GB of 64-bit wide DDR4 (2 x Bank of 4GB); 2*128 Mbytes of QSPI Flash for bit streams storage; 1*128 Mbytes of QSPI Flash for user data storage; one Xilinx Artix® -7 transceiver optimized FPGA.

From an interface point of view, the Kintex® UltraScale™ FPGA directly connects to the board’s backplane connectors via SERDES, LVDS and fiber, thus optimizing digital signal processing, packet processing and board transfer performance with achievable data rates of up to 16.3 Gbps. Up to 3*4-lane fabric ports are available on the board’s VPX connectors, configurable as either 3 * GTH x4 to Fat Pipes on the P1A and P1B VITA 66.4 connectors, or 3 * GTH x4 to 12 optical transceivers on the VITA 66.5 connector (12TRX). In addition, 28 FPGA GPIOs are made available on the P2 VITA 66.4 connector.

The board is delivered with host drivers and an example design including hardware IP Resources (VHDL code) that can be used to implement PCI Express Gen2/Gen3 links, 10 Gigabit Ethernet ports (XAUI, 10GBase-KR) and Xilinx Aurora. A VITA 57.4 compliant FMC+ site is available to plug in an FPGA Mezzanine Card (see our FMC modules range). Additional accessories include an Engineering kit (JTAG ports for FPGA configuration) and rear transition modules. From a firmware standpoint, the IC-FEP-VPX3f board is compatible with the Xilinx development tools (Vivado, platform cable).

The board is available in standard, air-cooled and conduction-cooled grades (85°C).

Interface Concept

www.interfaceconcept.com