DDC-I and LDRA Announce Integrated Tooling for DO-178C Testing for Deos RTOS Users

Deos/LDRA tool suite integration leverages unique RTOS instrumentation hooks to deliver enhanced timing analysis and Worst-Case Execution Time (WCET) test capability, applicable for high-design assurance systems and especially useful for multi-core system development.

DDC-I and LDRA announced an enhanced integration between the Deos safety-critical DO-178C certifiable RTOS and the LDRA tool suite. The integrated solution, qualified to Design Assurance Level A (DAL A), utilizes unique OS-level instrumentation hooks that enable the LDRA tool suite to deliver enhanced unit test and worst-case timing analysis capabilities.

Unlike conventional RTOS/unit test integrations, which utilize chip-level facilities such as special registers or timers, Deos provides process log events with high-resolution time stamps that link what’s going on at the process level with the kernel’s more uniform/consistent view of time. Using the developer’s interference generation tool, these OS-level hooks provide for WCET measurement at both the system and task level.

“DDC-I has been at the forefront of DO-178C safety-critical multi-core technology development, standardization, and verification, with an emphasis on the guidance of CAST-32A initially, and then more recently the January 2024 release of AC 20-193 Use of Multi-Core Processors,” said Greg Rose, vice president of marketing at DDC-I. “Integrating Deos with the LDRA tool suite gives avionics developers the unit test platform they need to identify and resolve complex multi-core timing issues, especially the worst-case execution scenarios critical to avionics.”

“Proving that an avionics system is properly partitioned to avoid interference from competing cores is critical, yet nearly impossible, without the proper development and testing tools,” said Ian Hennell, Operations Director at LDRA. “Deos provides OS-level hooks that give the LDRA tool suite unique visibility into RTOS operation, enabling it to deliver uniform timing analysis with enhanced worst-case execution capabilities, essential for airworthiness certification.”

About the LDRA tool suite

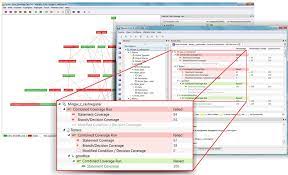

The LDRA tool suite is LDRA’s flagship platform that delivers open and extensible solutions for building quality into software from requirements through to deployment. The tool suite provides a continuum of capabilities, including requirements traceability, test management, coding standards compliance, code quality review, code coverage analysis, data-flow and control-flow analysis, unit/integration/target testing, and certification and regulatory support. The LDRA tool suite’s unit and integration testing capabilities provide an intuitive user interface that allows the same tests to be executed in the host or target environments. Where code reuse is considered, they allow those same tests to be re-run automatically in different target environments. Test generation (test harness, test vectors, code stubs) and result-capture support are available for various host and target platforms. Optimized instrumentation technology supports even highly constrained 8- and 16-bit microcontrollers and high-performance 32- and 64-bit processors.

TBwcet is an optional module for the LDRA tool suite that automates the measurement of WCET on the target – the only way to provide evidence of adequate resourcing and mitigation for interference where multi-core processors (MCP) are deployed. Test results and reports generated using TBwcet can be uploaded to LDRAvault. LDRAvault is a web application that automatically aggregates certification artifacts across distributed users and complex projects, can easily adapt to comply with a growing and evolving certification and regulatory landscape, supports traditional as well as CI/CD workflows, automatically generates advanced visualizations to gain insights across large and targeted sets of certification data through a ‘single pane of glass,’ and enables effective collaboration across the enterprise and supply chain, and with regulatory authorities.

About Deos

Deos is a safety-critical embedded RTOS that employs patented cache partitioning, memory pools, and safe scheduling to deliver higher CPU utilization than other certifiable safety-critical COTS RTOS on multi-core processors. First certified to DO-178 DAL A in 1998, Deos provides certified conformant FACE OSS Safety Base and Safety Extended Profiles that feature hard real-time response, time and space partitioning, with support for Rate Monotonic, ARINC-653, and POSIX interfaces.

SafeMC technology extends Deos’ advanced capabilities to multiple cores, enabling developers of safety-critical systems to achieve best-in-class multi-core performance without compromising safety-critical task response and guaranteed execution time. SafeMC employs a bound multiprocessing (BMP) extension of the symmetric multiprocessing architecture (SMP), safe scheduling, and cache partitioning to minimize cross-core contention and interference patterns that affect the performance, safety criticality, and certifiability of multi-core systems. These features enable avionics systems developers to address issues that could impact a software airborne system’s safety, performance, and integrity as specified by the FAA’s Advisory Circular (AC) AC 20-193.

Target Platforms

Deos and the LDRA tool suite are available for various popular avionics multi-core processors, including the NXP i.MX8. Other popular targets include the Xilinx XC102 and ZCU102 evaluation kit), x86, TI, and soon Qualcomm.